# UNIVERSIDADE FEDERAL DO AMAZONAS - UFAM INSTITUTO DE COMPUTAÇÃO - ICOMP PROGRAMA DE PÓS-GRADUAÇÃO EM INFORMÁTICA - PPGI

### Integração de Características Preemptivas à Técnica de Escalonamento Dinâmico de Tensões e Frequências Intra-Tarefa

por Rawlinson da Silva Gonçalves

> Manaus - Amazonas 10 de julho de 2015

#### PODER EXECUTIVO MINISTÉRIO DA EDUCAÇÃO UNIVERSIDADE FEDERAL DO AMAZONAS - UFAM INSTITUTO DE COMPUTAÇÃO - ICOMP PROGRAMA DE PÓS-GRADUAÇÃO EM INFORMÁTICA - PPGI

### Integração de Características Preemptivas à Técnica de Escalonamento Dinâmico de Tensões e Frequências Intra-Tarefa

por

Rawlinson da Silva Gonçalves

Dissertação apresentada ao Programa de Pós-Graduação em Informática do Instituto de Computação da Universidade Federal do Amazonas como requisito para a obtenção do grau de Mestre em Engenharia de Software e Sistemas Embarcados.

**Orientador:** Dr. Raimundo da Silva Barreto

Manaus - Amazonas 10 de julho de 2015

#### Ficha Catalográfica

Ficha catalográfica elaborada automaticamente de acordo com os dados fornecidos pelo(a) autor(a).

Goncalves, Rawlinson da Silva

G635i

Integração de Características Preemptivas à Técnica de Escalonamento Dinâmico de Tensões e Frequências Intra-Tarefa / Rawlinson da Silva Goncalves. 2015 160 f.: il. color; 29,7 cm.

Orientador: Raimundo da Silva Barreto Dissertação (Mestrado em Informática) - Universidade Federal do Amazonas.

1. Sistemas Embarcados. 2. Sistemas de Tempo Real. 3. DVFS Intra-Tarefa. 4. Redução do Consumo de Energia. 5. Tratamento de Preempções. I. Barreto, Raimundo da Silva II. Universidade Federal do Amazonas III. Título

#### PODER EXECUTIVO MINISTÉRIO DA EDUCAÇÃO INSTITUTO DE COMPUTAÇÃO

PROGRAMA DE PÓS-GRADUAÇÃO EM INFORMÁTICA

### FOLHA DE APROVAÇÃO

"Integração de Características Preemptivas à Técnica Escala Dinâmica de Voltagem e Frequência Intra-Tarefa"

### **RAWLINSON DA SILVA GONÇALVES**

Diessertação de Mestrado defendida e aprovada pela banca examinadora contituída pelos Professores:

Prof. Raimundo da Silva Barreto - PRESIDENTE

Mus Anduro

Prof. Lucas Carvalho Cordeiro - MEMBRO INTERNO

Prof. Rivalino Matias Júnior - MEMBRO EXTERNO

Manaus, 10 de Julho de 2015

#### Agradecimentos

Primeiramente a Deus por todos esses anos ter me proporcionado saúde, força e perseverança, para que eu pudesse percorrer todo esse caminho e ter chegado até aqui, mesmo diante de algumas "topadas" que levei durante essa jornada.

Aos meus pais, familiares e amigos que sempre acreditaram no meu potencial, me dando todo o apoio, carinho, atenção e incentivo para a realização dos meus sonhos. Gostaria de agradecer especialmente as minhas tias Maria Antônia, Inês e Luíza, ao tio José, aos meus primos Diego e Débora, a minha irmã Eliza e, principalmente, a minha mãe Joana por terem me ajudado a cuidar do meu pai ao longo desses anos, seja cuidando dele no dia-a-dia, levando-o para ter momento de lazer ou nas consultas médicas. Dessa forma, consegui ter mais tempo para me dedicar as atividades do mestrado, sabendo que ele estava em boas mãos.

Ao Prof. Dr. Raimundo da Silva Barreto, que ao longo desses anos contribuiu significativamente para minha formação acadêmica, profissional e pessoal, desde a graduação (meados de 2007). Acima de tudo, pelas orientações, conselhos, ensinamentos e críticas que foram primordiais para a conclusão desta dissertação.

Aos meus amigos Diego, Gabriel, Herbert, Spósito e Valentin, as minhas amigas Daniella e Odette (todos do laboratório GISE) que compartilharam seus conhecimentos como pesquisadores, para que eu amadurecesse mais rapidamente.

Aos meus amigos do Projeto da Samsung Anderson, Alberto, Erick, Larissa Ayres e Larissa Bentes pelos momentos de aprendizado e trabalho em equipe durante o desenvolvimento do projeto.

Aos meus amigos dos PPGI, em especial aos grupos ExperTS e Labotim, Nilmara, Bruno, Vitor, Rallyson, Juan, Jhonathan, Anderson e Rayner pelas horas de estudo e aprendizado.

Enfim, a todos pelos momentos únicos de descontração durante as refeições, lanches e happy hours, sempre mostrando companheirismo e amizade.

À FAPEAM pelo apoio financeiro. A UFAM por prover a infraestrutura necessária para o desenvolvimento desta dissertação. Aos meus amigos da secretaria do PPGI Elienai, Frank e Helen pela ajuda com os procedimentos administrativos e documentações referentes ao mestrado.

Principalmente, a todos que me deram o apoio necessário para ajudar a amenizar a perda do meu Pai, Carlos Gonçalves Viana (em memória), que fique registrado: Ele foi um grande homem. Não tinha muito estudo, mas era muito sábio e tinha uma visão única de ver o mundo e as pessoas.

A todos os demais professores, onde tive o privilégio de ser aluno e que também tiveram sua parcela de contribuição para que eu fosse capaz de concluir esta dissertação.

Enfim, a todos que direta ou indiretamente puderam contribuir para o desenvolvimento desta dissertação. Meu muito obrigado!

#### RESUMO

Os sistemas embarcados têm evoluído significativamente nos últimos anos, principalmente devido aos avanços da tecnologia, a redução dos custos dos equipamentos eletrônicos e a popularização dos dispositivos móveis. Muitos desses sistemas dependem da energia provenientes de baterias para manter o funcionamento dos seus diversos componentes. No entanto, para que esses dispositivos tenham uma boa autonomia, várias técnicas e metodologias têm sido propostas para melhor gerenciar o consumo de energia do sistema como um todo. Essa necessidade tem contribuído para o surgimento de diversas linhas de pesquisa, principalmente na área de sistemas de tempo real, onde o fator complicante não está somente em reduzir o consumo de energia, mas também em respeitar as restrições temporais de todas as tarefas em execução no sistema.

Sendo assim, este trabalho tem como objetivo diminuir o consumo de energia do processador utilizando a técnica de escalonamento dinâmico de tensões e frequências do processador intra-tarefa, também conhecido como DVFS intra-tarefa (em inglês, Dynamic Voltage and Frequency Scaling). A metodologia online proposta visa realizar o gerenciamento das trocas de tensões e frequências do processador, através de uma abordagem colaborativa entre as aplicações de tempo real e o sistema operacional. Dessa forma, ambos podem trabalhar em conjunto, dentro do núcleo do sistema, para diminuir os tempos de resposta dos chaveamentos de tensões e frequências do processador, principalmente diante de sucessivas preempções entre as aplicações de tempo real em execução no sistema. Os resultados experimentais dessa metodologia, utilizando o C-Benchmarck, mostraram que é possível diminuir cerca de 6% o consumo de energia do processador, mesmo executando todas as tarefas no pior caso.

Palavras-Chave: Sistemas Embarcados, Sistemas de Tempo Real, DVFS Intra-Tarefa, Redução do Consumo de Energia, Tratamento de Preempções.

#### ABSTRACT

Embedded systems have evolved significantly in recent years, mainly due to advances in technology, cost reduction of electronic equipment, and mainly the popularization of mobile devices. Many of these systems require energy resources from battery to maintain the operation of their various components. However, for these devices to have a good autonomy, several techniques and methodologies have been implemented to better manage energy consumption of the system as a whole. This need has contributed to the rise of various lines of research, mainly in the area of real-time systems, where the complicating factor is not only reducing energy consumption but also respect the time constraints of all tasks running on the system.

Thus, this work aims to maximize energy gains from the use of intra-task dynamic voltage and frequency scaling technique, also known as intra-task DVFS. The proposed online methodology aims to achieve better management of exchanging voltages and frequency of the processor, through a collaborative approach between real-time applications and the operating system. Therefore, both can work together, within the kernel of the system, to reduce the response times of the processor context switches, mainly after preemptions. The experimental results, using the C-Benchmarck, showed that it is possible to decrease about 6% processor power consumption even performing all tasks in the worst case.

**Keywords:** Embedded Systems, Real Time Systems, DVFS Intra-Task, Low Power Consumption, Preemptions Treatment.

### Sumário

| Li       | sta d | le Figu | ıras                                            |   | xi  |

|----------|-------|---------|-------------------------------------------------|---|-----|

| Li       | sta d | le Tab  | elas                                            |   | xv  |

| Li       | sta d | le Algo | oritmos                                         | X | vii |

| Li       | sta d | le Cód  | ligos Fonte                                     | 2 | xix |

| Li       | sta d | le Abr  | eviações e Acrônimos                            | 2 | xxi |

| 1        | Intr  | roduçã  | .0                                              |   | 1   |

|          | 1.1   | Descri  | ição do Problema                                |   | 3   |

|          | 1.2   | Conte   | xto                                             |   | 4   |

|          | 1.3   | Motiv   | ação e Justificativa                            |   | 5   |

|          | 1.4   | Objeti  | ivos                                            |   | 5   |

|          | 1.5   | Métod   | do Proposto                                     |   | 6   |

|          | 1.6   | Organ   | nização do Trabalho                             |   | 7   |

| <b>2</b> | Cor   | ceitos  | e Definições                                    |   | 9   |

|          | 2.1   | Sistem  | nas Embarcados                                  |   | 9   |

|          | 2.2   | Sistem  | nas de Tempo Real                               | • | 9   |

|          |       | 2.2.1   | Modelo de Tarefas e suas Propriedades Temporais |   | 10  |

|          |       | 2.2.2   | Relação de Precedência e de Exclusão Mútua      |   | 11  |

|          |       | 2.2.3   | Algoritmo de Escalonamento                      |   | 11  |

|          |       | 2.2.4   | Teste de Escalonabilidade                       |   | 13  |

|          | 2.3   | Escalo  | onamento Dinâmico de Tensão e Frequência (DVFS) |   | 20  |

|          | 2.4   | Grafo   | de Fluxo de Controle                            |   | 21  |

viii SUMÁRIO

|   | 2.5  | Kerne  | l do Linux                            | 22 |

|---|------|--------|---------------------------------------|----|

|   |      | 2.5.1  | Escalonador                           | 23 |

|   |      | 2.5.2  | Chamadas de Sistema                   | 24 |

|   |      | 2.5.3  | Módulo CPUFreq                        | 24 |

|   | 2.6  | RTAI   |                                       | 25 |

|   | 2.7  | Resum  | 10                                    | 27 |

| 3 | Tral | balhos | Correlatos                            | 29 |

|   | 3.1  | Planej | amento da Revisão Sistemática         | 30 |

|   | 3.2  | Condu  | ıção da Revisão Sistemática           | 32 |

|   | 3.3  | Anális | e dos Resultados                      | 38 |

|   |      | 3.3.1  | Metodologias Online                   | 38 |

|   |      | 3.3.2  | Metodologias Offline                  | 39 |

|   |      | 3.3.3  | Metodologias Híbridas                 | 44 |

|   |      | 3.3.4  | Análises Quantitativas                | 47 |

|   |      | 3.3.5  | Análises Qualitativas                 | 49 |

|   | 3.4  | Resum  | 10                                    | 52 |

| 4 | Rau  | v Gove | ernor                                 | 55 |

|   | 4.1  | Defini | ções e Modelos Adotados               | 56 |

|   |      | 4.1.1  | Modelo do Sistema e Modelo de Tarefas | 56 |

|   |      | 4.1.2  | Modelos de Overhead                   | 57 |

|   |      | 4.1.3  | Modelo de Energia                     | 58 |

|   | 4.2  | Model  | agem do Método Proposto               | 59 |

|   |      | 4.2.1  | Chamadas de Sistema do Raw Governor   | 61 |

|   |      | 4.2.2  | Raw Governor                          | 61 |

|   |      | 4.2.3  | Raw Monitor                           | 63 |

|   | 4.3  | Metod  | lologia                               | 64 |

|   | 4.4  | Resum  | 10                                    | 68 |

| 5 | Res  | ultado | s Experimentais                       | 69 |

|   | 5.1  | Ambie  | ente de Experimentação                | 69 |

|   | 5.2  | Config | guração do <i>Hardware</i>            | 70 |

SUMÁRIO ix

|              | 5.3   | Definição dos <i>Benchmarks</i> e dos Estudos de Caso | 71  |

|--------------|-------|-------------------------------------------------------|-----|

|              | 5.4   | Resultados Experimentais                              | 75  |

|              | 5.5   | Resumo                                                | 79  |

| 6            | Con   | ıclusões                                              | 81  |

|              | 6.1   | Contribuições                                         | 82  |

|              | 6.2   | Pontos Limitantes                                     | 83  |

|              | 6.3   | Trabalhos Futuros                                     | 84  |

| Re           | eferê | ncias Bibliográficas                                  | 85  |

| A            | Pro   | cesso de instalação do ambiente de experimentação     | 91  |

| В            | Cha   | amadas de Sistema do $Raw\ Governor$                  | 101 |

| $\mathbf{C}$ | Feri  | ramenta Smartenum                                     | 103 |

| D            | Test  | te de escalonabilidade feito no MatLab                | 105 |

| $\mathbf{E}$ | Pro   | cesso de geração dos resultados experimentais         | 119 |

| $\mathbf{F}$ | Exe   | mplos dos relatórios gerados pelo CPUSTAT             | 127 |

# Lista de Figuras

| 1.1 | visão gerai da contextuanzação do trabamo, baseada na arquitetura do          |    |

|-----|-------------------------------------------------------------------------------|----|

|     | Linux proposta no livro de Love (2010)                                        | 4  |

| 1.2 | Visão geral da arquitetura proposta                                           | 7  |

| 2.1 | Visão geral das premissas temporais associadas a uma tarefa de tempo real.    | 11 |

| 2.2 | Exemplo de uma escala de tarefas $J_i$ utilizando a política de escalonamento |    |

|     | Rate-Monotonic (Cheng, 2002)                                                  | 13 |

| 2.3 | Representação da escala de execução das tarefas $\tau_1, \tau_2$ e $\tau_3$   | 19 |

| 2.4 | Processo de extração do grafo de fluxo de controle de uma aplicação, onde:    |    |

|     | (a) Mostra o seu código fonte; (b) O CFG extraído a partir do código          |    |

|     | fonte e seus componentes básicos; e (c) Mostra o processo de análise da       |    |

|     | quantidade de ciclos de execução da tarefa no pior caso (Shin e Kim, 2001).   | 22 |

| 2.5 | Visão geral dos principais componentes e recursos do Kernel do Linux          |    |

|     | utilizados nesta dissertação                                                  | 23 |

| 2.6 | Visão geral do processo de execução de uma chamada de sistema no Linux        |    |

|     | (Cheng, 2002)                                                                 | 24 |

| 2.7 | Arquitetura do RTAI e seus principais componentes<br>(Bergsma, 2009)          | 26 |

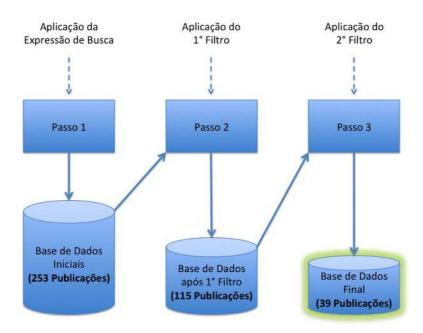

| 3.1 | O diagrama mostra uma visão global do processo de seleção das                 |    |

|     | publicações e uma analise quantitativa de cada etapa.                         | 32 |

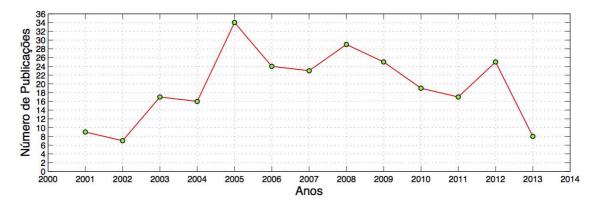

| 3.2 | Número de publicações por ano                                                 | 33 |

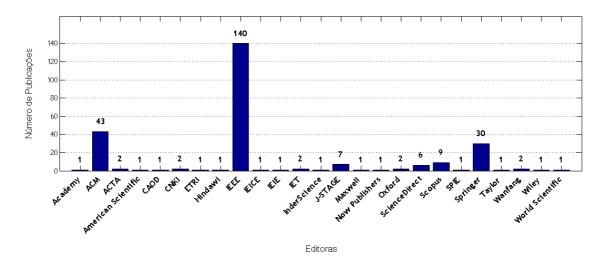

| 3.3 | Número de publicações por editora                                             | 34 |

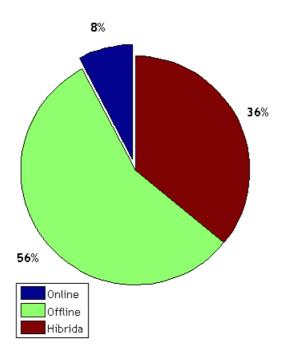

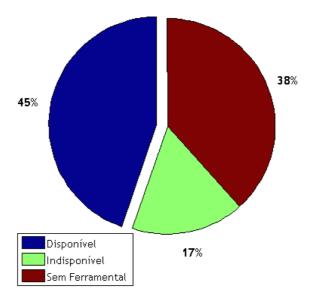

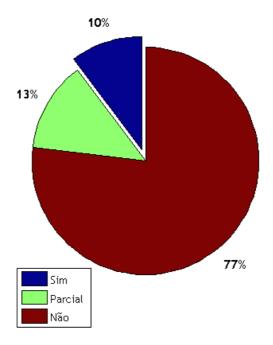

| 3.4 | Análise quantitativa dos modos de execução das técnicas catalogadas           | 48 |

| 3.5 | Analise quantitativa da disponibilidade ferramental das publicações           |    |

|     | catalogadas                                                                   | 48 |

| 3.6 | Análise quantitativa das técnicas que dão suporte a preempções                | 49 |

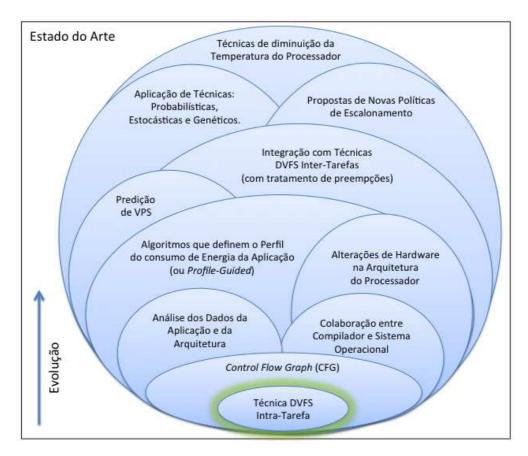

| 3.7 | O diagrama mostra uma visao mais abrangente da evolução do estado da                                          |    |

|-----|---------------------------------------------------------------------------------------------------------------|----|

|     | arte na área de baixo consumo de energia, do ponto de vista da técnica                                        |    |

|     | DVFS intra-tarefa                                                                                             | 52 |

| 4.1 | Exemplo de uma tarefa de tempo real, onde: (a) mostra o código fonte;                                         |    |

|     | (b) mostra o processo de inserção de pontos de controle ( $\mathit{CKs}$ ), proposto                          |    |

|     | por Yi $\operatorname{et}$ $\operatorname{al.}$ (2005); e (c) o CFG extraído a partir do código fonte do item |    |

|     | b, onde as arestas contém os custos computacionais de cada caminho no                                         |    |

|     | pior caso.                                                                                                    | 58 |

| 4.2 | Modelagem do método proposto                                                                                  | 60 |

| 4.3 | O código mostra um exemplo de como as aplicações passam informações                                           |    |

|     | locais ao sistema operacional                                                                                 | 66 |

| 4.4 | Método proposto por AbouGhazaleh et al. (2003b)                                                               | 66 |

| 4.5 | Visão geral das trocas de mensagens entre as técnicas que realizam o                                          |    |

|     | tratamento de preempção no espaço do usuário e no núcleo do sistema                                           | 67 |

| 5.1 | Exemplo do processo de inserção de 3 VSPs no código fonte da aplicação,                                       |    |

|     | onde: (a) mostra o código fonte original; (b) mostra o processo de divisão                                    |    |

|     | dos blocos de código da aplicação; e (c) mostra a inserção das VSPs em                                        |    |

|     | cada bloco                                                                                                    | 75 |

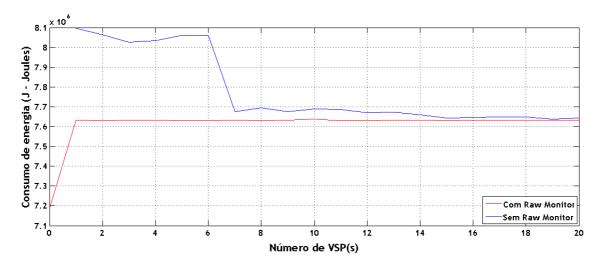

| 5.2 | ${\cal O}$ gráfico mostra o consumo de energia dinâmica do processador em função                              |    |

|     | do número de VSPs com e sem a atuação do Raw Monitor                                                          | 76 |

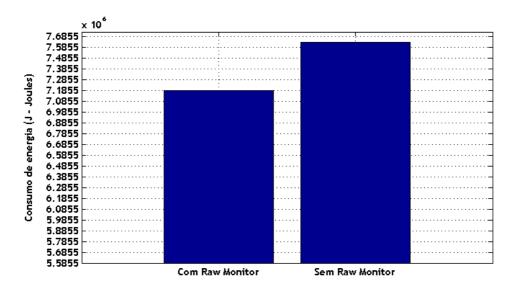

| 5.3 | O gráfico em barras mostra o consumo de energia final do processador                                          |    |

|     | com e sem a atuação do Raw Monitor                                                                            | 77 |

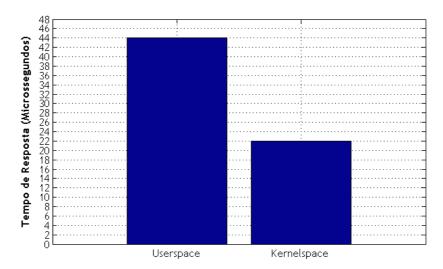

| 5.4 | O gráfico mostra a comparação entre o tempo de resposta do chaveamento                                        |    |

|     | de contexto do processador entre o espaço do usuário e o núcleo do sistema.                                   | 78 |

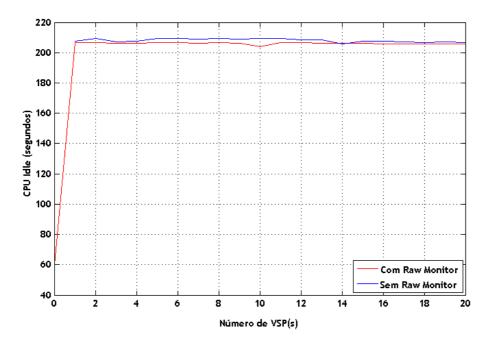

| 5.5 | O gráfico mostra o tempo ocioso do processador em função do número de                                         |    |

|     | VSPs com e sem a atuação do $Raw\ Monitor.$                                                                   | 78 |

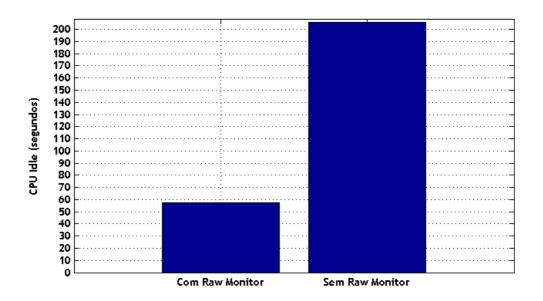

| 5.6 | O gráfico em barras mostra o tempo ocioso final do processador com e                                          |    |

|     | sem a atuação do Raw Monitor                                                                                  | 79 |

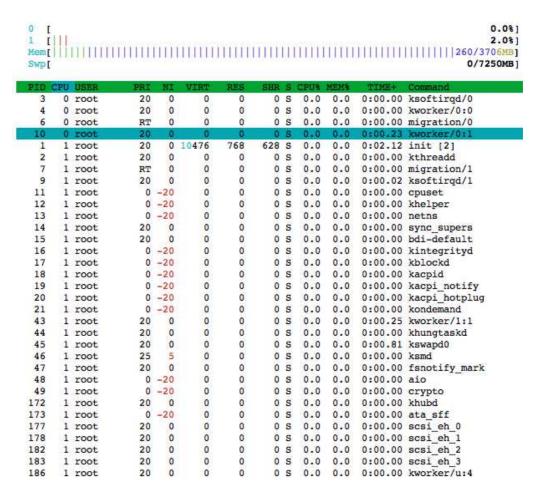

| A.1 | Lista de tarefas em execução em cada núcleo do processador, durante o                                         |    |

|     | carregamento inicial do ambiente de experimentação                                                            | 93 |

| F.1 | Exemplo do relatório estatístico do processador gerado pelo CPUSTAT 1                                         | 27 |

LISTA DE FIGURAS xiii

| F.2 | Exemplo | do | relatório | estatístico | das | tarefas | de | tempo | real | gerado | pelo | )     |

|-----|---------|----|-----------|-------------|-----|---------|----|-------|------|--------|------|-------|

|     | CPUSTA' | Т. |           |             |     |         |    |       |      |        |      | . 128 |

### Lista de Tabelas

| 2.1 | Lista de tensões e frequências do processador $AMD\ Athlon\ II\ X2\ 250.$     | 21 |

|-----|-------------------------------------------------------------------------------|----|

| 3.1 | Nome completo das editoras sem abreviações                                    | 34 |

| 3.2 | Publicações que compõem a base de dados final da revisão sistemática          |    |

|     | (Parte 1)                                                                     | 35 |

| 3.3 | Publicações que compõem a base de dados final da revisão sistemática          |    |

|     | (Parte 2)                                                                     | 36 |

| 3.4 | Publicações que compõem a base de dados final da revisão sistemática          |    |

|     | (Parte 3)                                                                     | 37 |

| 3.5 | Lista de métricas estabelecidas para realizar a comparação de                 |    |

|     | completude entre as publicações que compõem a base de dados final da          |    |

|     | revisão sistemática                                                           | 50 |

| 3.6 | Critérios de classificação das publicações selecionadas no $2^{\rm o}$ filtro | 51 |

| 3.7 | Comparação de completude entre as abordagens pertencentes a base de           |    |

|     | dados final da revisão sistemática.                                           | 51 |

| 5.1 | Lista de tarefas que compõem o estudo de caso desta dissertação               | 72 |

| 5.2 | Lista dos 41 casos de teste que compõem o processo de validação do            |    |

|     | método proposto (parte 1)                                                     | 74 |

| 5.3 | Mostra o consumo de energia e o tempo ocioso do processador para cada         |    |

|     | um dos 41 casos de teste (dados ordenados pelas colunas 2 e 4 em destaque).   | 76 |

# Lista de Algoritmos

| 1 | Pseudocódigo utilizado pelo $Raw\ Governor$ para realizar o tratamento de |

|---|---------------------------------------------------------------------------|

|   | preempções                                                                |

| 2 | Pseudocódigo utilizado para estabelecer comunicação entre o escalonador   |

|   | do sistema operacional e o Raw Governor                                   |

## Lista de Códigos Fonte

| 3.1 | Expressão de busca utilizada na Scopus para realizar a coleta das 253           |    |

|-----|---------------------------------------------------------------------------------|----|

|     | publicações retornadas na fase inicial da revisão sistemática                   | 32 |

| A.1 | Política padrão do <i>cgroups</i> para o ambiente de experimentação             | 92 |

| A.2 | Regra padrão do <i>cgrules</i> para o ambiente de experimentação                | 92 |

| A.3 | Os novos atributos adicionados na estrutura de dados da tarefa dentro do        |    |

|     | Kernel do Linux                                                                 | 94 |

| A.4 | Esse trecho de código direciona as tarefas do sistema operacional para o        |    |

|     | segundo núcleo do processador, deixando o primeiro núcleo exclusivo para        |    |

|     | as aplicações de tempo real                                                     | 95 |

| A.5 | Esse trecho de código direciona as novas tarefas do sistema operacional,        |    |

|     | que não sejam de tempo real, para o segundo núcleo do processador               |    |

|     | garantindo que o primeiro núcleo seja usado apenas por aplicações de            |    |

|     | tempo real (criadas pelo RTAI)                                                  | 95 |

| A.6 | Função utilizada pelo $Raw\ Governor$ para validar e obter frequências          |    |

|     | validas do processador                                                          | 95 |

| A.7 | Função utilizada pelo $Raw\ Governor$ para definir novas frequências no         |    |

|     | processador                                                                     | 96 |

| A.8 | Essa função é uma extensão do $Raw\ Monitor$ dentro do $Raw\ Governor$          |    |

|     | cujo objetivo é realizar o monitoramento das tarefas de tempo real que          |    |

|     | estão retornando de preempção de acordo com as instruções passadas pelo         |    |

|     | escalonador do sistema.                                                         | 97 |

| A.9 | Esta função foi inserida dentro do escalonador do RTAI para alertar o $\it Raw$ |    |

|     | Monitor sobre as tarefas que estão retornando de preempção                      | 98 |

| A.10 | Trecho de código é responsável por aplicar o Raw Governor ao primeiro           |

|------|---------------------------------------------------------------------------------|

|      | núcleo do processador durante a chamada da função de inicialização do           |

|      | RTAI                                                                            |

| C.1  | Exemplo de dados de entrada da ferramenta Smartenum (layout do                  |

|      | arquivo de entrada está descrito no manual da ferramenta) 103                   |

| C.2  | Exemplo dos dados de saída gerados pela ferramenta Smartenum 104                |

| D.1  | Resultado da utilização do processador com base nos dados calculados            |

|      | pela ferramenta Smartenum                                                       |

| D.2  | Script implementado no Mat<br>Lab para realizar o teste de escalonabilidade     |

|      | interativo baseado na Equação 2.25                                              |

| D.3  | Resultado gerado após a execução do Código D.2                                  |

| E.1  | Shell Script feito para automatizar a geração dos resultados experimentais. 119 |

### Lista de Abreviações e Acrônimos

ACEP Average-Case Execution Path

ACM The Association for Computing Machinery

API Application Programming Interface

AVS Automatic Voltage Scaler

BSORT Bubble Sort

DVFS Dynamic Voltage and Frequency Scaling

DVS Dynamic Voltage Scaling

CDVS Combined DVS

CDVS-NS CDVS No Sleep State

CDVS-S CDVS Sleep State

CFG Control-Flow Graph

CHP Common Hot Path

CK Checkpoint

CNT Count

CMOS Complementary Metal-Oxide-Semiconductor

CPU Central Processing Unit

CPUID CPU IDentification

CPUSTAT CPU Statistic

EDF Earliest Deadline First

FPPT Fixed-Priority scheduling with Preemption Threshold

HAL Hardware Abstraction Layer

ID IDentification

IEEE The Institute of Electrical and Electronics Engineers

IntraDVS Intra Dynamic Voltage Scaling

IO Input and Output

IPC Inter-Process Communication

ItcaEDF Intra-Task Characteristics Aware EDF

MOSFET Metal Oxide Semiconductor Field Effect Transistor

MRTC Mälardalen Real Time Research Centre

VSP Voltage Scaling Point

PCP Priority Ceiling Protocol

PID Process Identifier

PMH Power Management Hint

PMP Power Management Point

pWCEC Probabilistic Worst-Case Execution Cycle RAEP Remaining Average-Case Execution Path

RM Rate-Monotonic

RMS Rate-Monotonic Scheduler

ROEP Remaining Optimal-Case Execution Path

RT Real Time

RTAI Real-Time Application Interface

RTLPower Real-Time Low Power

RWCEC Remaining Worst Case Execution Cycle

RWEP Remaining Worst-Case Execution Path

SEC Saved Execution Cycles

TALk Temperature Aware Leakage

UID User IDentification

VSP Voltage Scaling Point

WCEC Worst Case Execution Cycle

WCEP Worst Case Execution Path

WCET Worst Case Execution Time

WCR Worst-Case Remaining

### Capítulo 1

### Introdução

Os avanços da tecnologia e a redução dos custos dos equipamentos eletrônicos proporcionaram uma maior popularização dos sistemas embarcados. Isso fez com que esses dispositivos passassem a estar cada vez mais presentes no cotidiano das pessoas, principalmente pela mobilidade, facilidade ao acesso à informação, comunicação, entre outros benefícios. Dessa forma, a necessidade por maior capacidade de processamento, maior autonomia de bateria e redução do consumo de energia vêm crescendo significativamente nos últimos anos (Pillai e Shin, 2001).

Essas necessidades têm gerado diversas linhas de pesquisa, principalmente, na área de baixo consumo de energia, que tem se tornado uma métrica importante de qualidade no projeto de sistemas embarcados e sistemas de tempo real (Alipour et al., 2011; Cohen et al., 2012). Uma das técnicas mais utilizadas para reduzir o consumo de energia é o escalonamento dinâmico de tensões e frequências (em inglês, *Dynamic Voltage and Frequency Scaling* - DVFS) que possibilita alterar em tempo de execução, via software, a tensão e frequência do processador de acordo com alguma política pré-definida, sendo possível ainda gerenciar o consumo de energia (Kim et al., 2008; Baums e Zaznova, 2008).

Dentro do Kernel do Linux, a técnica DVFS é implementada através dos Governors. Os Governors são políticas predefinidas responsáveis por realizar o gerenciamento das tensões e frequências que serão utilizadas pelo processador. A grande maioria dessas políticas funciona por meio da análise da carga de trabalho do sistema, dentro de uma determinada janela de tempo pré-definida. Esse aspecto tornam os Governors reativos, pois necessitam analisar informações que ocorreram no passado para poder estimar a frequência que deverá ser aplicada sobre o processador, a fim de atender as demandas computacionais exigidas pelos programas em execução no sistema (Love, 2010). Dentre todos os Governors presentes no Kernel do Linux, o Userspace Governor é a única política que permite as aplicações definirem as tensões e frequências que deverão ser utilizadas pelo processador. Sendo assim, não há um canal de comunicação efetivo entre

as aplicações e o *Governor*, de modo que o *Governor* possa ter o controle das tensões e frequências utilizadas por cada uma das tarefas em execução no sistema.

Dentro do contexto de sistemas de tempo real, o uso da técnica de baixo consumo de energia dentro das aplicações é conhecido como DVFS intra-tarefa, cujo principal objetivo é fornecer às aplicações um conjunto de ferramentas para controlar as tensões e frequências do processador, mesmo estando no espaço do usuário (Shin et al., 2001a). Essa técnica deu origem a várias outras técnicas, cujo o cerne é analisar o código fonte da aplicação e encontrar os melhor lugares para inserir esses pontos de chaveamento de tensões e frequências, de forma que haja redução no consumo de energia do processador (Takase et al., 2011; Tatematsu et al., 2011; Mohan et al., 2010; Yang et al., 2009; Zitterell e Scholl, 2008).

A técnica mais difundida na literatura é feita através da análise do grafo de fluxo de controle (em inglês, Control-Flow Graph - CFG) da aplicação e, em seguida, são extraídos os pontos do código onde deverão ser inseridos os pontos de controle (em inglês, Checkpoints ou também chamado de Voltage Scaling Point - VSP) (Shin e Kim, 2001; Shin et al., 2001a; Lee et al., 2002; Shin et al., 2001b; Buss et al., 2003; Seo et al., 2004). Os pontos de controle são trechos de código responsáveis por realizar as trocas de tensões e frequências do processador de acordo com a necessidade da aplicação. O principal ganho dessa metodologia está na detecção de trechos de código que deixaram de ser executados, dependendo do fluxo de execução da aplicação (exemplo: estruturas de repetição que deixaram de executar algumas interações, pois suas condições de término foram atendidas antes de alcançar o número máximo de interações). Dessa forma, os ganhos identificados são repassados para o processador, diminuindo a carga de processamento e, consequentemente, o consumo de energia (Shin et al., 2001a).

Essa metodologia tem diversas aplicabilidades quando consideramos um contexto de Sistemas de Tempo Real com múltiplas tarefas, pois além de diminuir o consumo de energia é possível diminuir o tempo ocioso do processador, sem violar as premissas temporais das tarefas em execução no sistema (Shin et al., 2001a). Dentro desse contexto, o menor consumo de energia será obtido quando o tempo de computação de cada tarefa for o mais próximo possível do seu deadline, pois dessa forma é possível obter o menor tempo ocioso do processador utilizando tensões e frequências ideais de acordo com a tarefa em execução.

A problemática desse cenário está no tratamento de preempções, pois o sistema operacional não fornecem chamadas de sistema para que as aplicações possam realizar o tratamento eficiente desse tipo de interrupção, como por exemplo: ajustar as tensões e frequências do processador já levando em consideração o tempo em que a tarefa ficou preemptada. Portanto, o objetivo central desta dissertação é diminuir o consumo de energia do processador, através da criação de um novo canal de comunicação entre as aplicações de tempo real e o controlador de tensões e frequências do processador do

sistema operacional, com o intuito de maximizar os ganhos da técnica DVFS intra-tarefa, através do melhor gerenciamento e tratamento de preempções entre as tarefas de tempo real em execução no sistema.

#### 1.1 Descrição do Problema

O baixo consumo de energia tem se tornado uma importante métrica dentro de sistemas de tempo real, mas precisa ser implementada com cautela, pois necessita garantir que todas as premissas temporais das aplicações em execução no sistema sejam respeitadas (Cohen et al., 2012). Nesse cenário, o menor consumo de energia será obtido com a utilização de tensões e frequências ideais para cada tarefa que venha a ser executada no sistema. Essas tensões e frequências ideias garantem que cada tarefa termine o seu processamento antes do seu deadline, deixando o processador o menor tempo possível ocioso (Awan e Petters, 2012; Cohen et al., 2012; Tatematsu et al., 2011; Mohan et al., 2010).

Esse cenário se torna ainda mais complexo quando consideramos múltiplas tarefas preemptivas e um escalonamento baseado em prioridade fixa, pois é necessário realizar testes de escalonabilidade para saber se um dado grupo de tarefas é ou não escalonável. Neste caso, diferentes variáveis devem ser levadas em consideração como as interferências ocasionadas por tarefas de maior prioridade; o tempo de processamento das tarefas no pior caso; o cálculo das tensões e frequências que deverão ser utilizadas por cada tarefa; entre outros (Cohen et al., 2012; Mohan et al., 2010).

Um dos grandes problemas é manter as tarefas executando o maior tempo possível usando suas tensões e frequências ideais diante da ocorrência de preempções, pois as tarefas não conseguem realizar o tratamento desse tipo de evento de forma eficiente, principalmente quando é analisado o tempo de resposta para o restabelecimento das tensões e frequências ideais das tarefas que está retornando de preempção. Esse fator se torna mais agravante devido à inexistência de uma canal de comunicação entre as aplicações de tempo real e o controlador de tensões e frequência do processador do sistema operacional.

O problema a ser tratado nesta dissertação pode ser expresso pela seguinte pergunta: é possível reduzir o consumo de energia do processador através da criação de uma abordagem colaborativa entre as aplicações de tempo real e o sistema operacional de forma que ambos possam trabalhar em conjunto no restabelecimento eficiente das tensões e frequências do processador principalmente diante de preempções?

#### 1.2 Contexto

O contexto desta dissertação está em criar um canal de comunicação mais efetivo entre as aplicações de tempo real e o controlador de tensões e frequências do processador do sistema operacional de forma que ambos possam trabalhar em conjunto, a fim de trazer parte do controle das tensões e frequências das aplicações para dentro do núcleo do sistema e diminuir o tempo de resposta do chaveamento de contexto do processador, principalmente no momento que as tarefas preemptadas retornam para o estado executando. Isso irá garantir que as tarefas executem por mais tempo utilizando suas tensões e frequências ideais, proporcionando a técnica DVFS intra-tarefa o suporte a preempções.

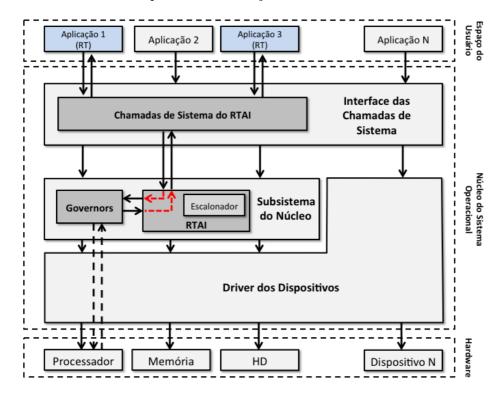

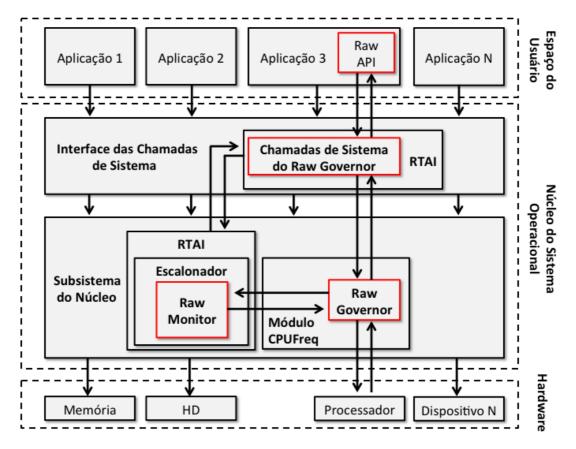

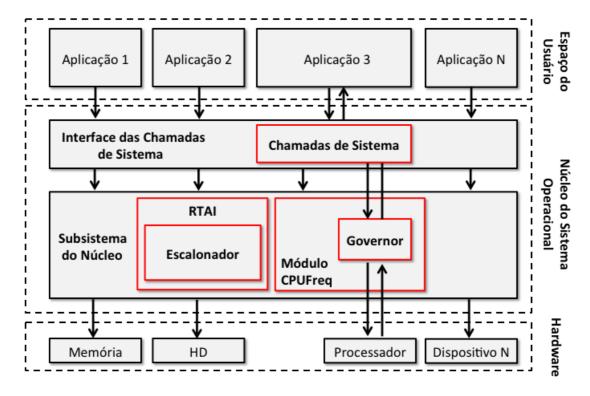

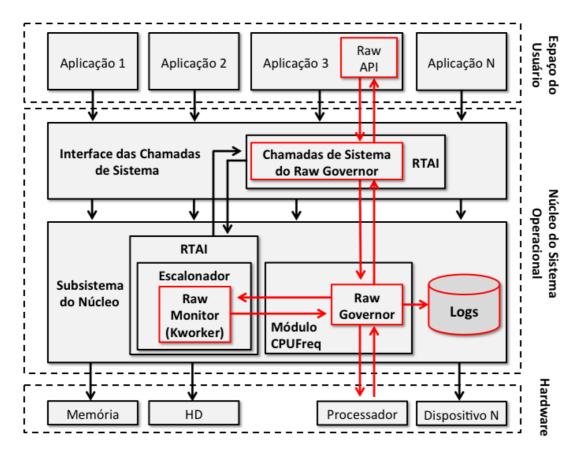

A Figura 1.1 mostra uma visão macro, por camadas, dos canais de comunicação existentes no *Kernel* do Linux, onde as características de tempo real são garantidas pela ferramenta RTAI (em inglês, *Real-Time Application Interface*), que por sua vez é responsável em gerenciar as tarefas de tempo real em execução no sistema.

Figura 1.1: Visão geral da contextualização do trabalho, baseada na arquitetura do Linux proposta no livro de Love (2010).

Essa arquitetura deixa mais evidente os problemas relatados na Seção 1.1, onde:

1. Os Governors existentes no Kernel do Linux não têm acesso aos dados das aplicações que estão em execução no sistema operacional e nem fornecem uma API para que elas possam trocar informações em tempo de execução (como por exemplo: as tensões e frequências ideais de cada aplicação);

2. A arquitetura mostra também que os *Governors* não têm um canal de comunicação com o escalonador do sistema para realizar o tratamento de preempções.

#### 1.3 Motivação e Justificativa

O projeto e desenvolvimento de sistema embarcados são complexos e precisam atender um conjunto de restrições, como por exemplo: tamanho, custo, consumo de energia, entre outros requisitos. Dentre os vários componentes presentes nesse tipo de sistema, o processador é o responsável por consumir grande parte dos recursos energéticos, principalmente devida a grande maioria deles utilizarem a tecnologia CMOS (em inglês, Complementary Metal-Oxide-Semiconductor) onde o consumo de energia ocorre nos pulsos de relógio de entrada na CPU e parte da energia é dissipada por seus milhares de transistores (Lee e Krishna, 1999). A Equação 1.1 define uma aproximação do consumo de energia dinâmica do processador segundo Shin et al. (2001a).

$$E \propto C_l \times N_{cycle} \times V_{dd}^2$$

(1.1)

Onde  $C_l$  é a capacitância de carga,  $N_{cycle}$  é o número de ciclos executados e  $V_{dd}^2$  é a tensão fornecida. Analisando a Equação 1.1, a tensão aplicada sobre o processador, por ser um termo quadrático, irá demandar maior quantidade de energia. Portanto desenvolver um controle mais refinado sobre essa variável implicará diretamente na diminuição quadrática do consumo de energia do dispositivo Shin et al. (2001b). Essas características tornam a técnica DVFS uma poderosa ferramenta na redução do consumo de energia do processador (Cohen et al., 2012; Tatematsu et al., 2011; Takase et al., 2011; AbouGhazaleh et al., 2003b; Shin et al., 2001b).

Esses motivos levaram ao desenvolvimento desta dissertação, onde o foco principal de pesquisa convergiu para redução do consumo de energia do processador por meio da integração de características preemptivas à técnica DVFS intra-tarefa.

# 1.4 Objetivos

O objetivo geral desta proposta é diminuir o consumo de energia do processador através da criação de uma abordagem colaborativa entre as aplicações de tempo real e o núcleo do sistema operacional, procurando reduzir o tempo de resposta do chaveamento das tensões e frequências do processador, principalmente no instante em que as tarefas preemptadas retornam para o estado de executando.

Sendo assim, o objetivo geral decompõe-se nos seguintes objetivos específicos:

- Prover um canal de comunicação entre as aplicações de tempo real e o controlador de tensões e frequências do processador do sistema operacional, a fim de que ambos possam trabalhar em conjunto na redução do consumo de energia do processador;

- 2. Reduzir o tempo de resposta de chaveamento de contexto do processador migrando o controle da técnica DVFS de dentro das aplicações para o núcleo do sistema operacional. Dessa forma, o sistema operacional passa a ter o controle das tensões e frequências que serão utilizadas no processador, com base nos dados informados pelas aplicações, e, além disso, introduzindo o tratamento de preempções à técnica DVFS intra-tarefa;

- 3. Demonstrar experimentalmente que a metodologia proposta é capaz de reduzir o consumo de energia do processador e maximizar os ganhos obtidos com a técnica DVFS intra-tarefa diante de preempções.

#### 1.5 Método Proposto

O método proposto nesta dissertação visa resolver os problemas apresentados nas Seções 1.1 e 1.2 cujo foco principal é fornecer à técnica DVFS intra-tarefa o suporte a preempções e um chaveamento de contexto do processador com menos *overheads*<sup>1</sup>, de acordo com a aplicação em execução no sistema, trazendo o gerenciamento e o controle das tensões e frequências do processador de dentro das aplicações em tempo real para dentro do núcleo do sistema operacional de forma que as tomadas de decisão sejam feitas com um menor tempo de resposta.

Em resumo, o cerne da solução proposta está em uma reestruturação do núcleo do sistema operacional de forma que o *Governor*, o escalonador e as aplicações de tempo real possam trabalhar em conjunto para prover uma solução eficiente aos problemas apresentados e reduzir o consumo de energia do processador.

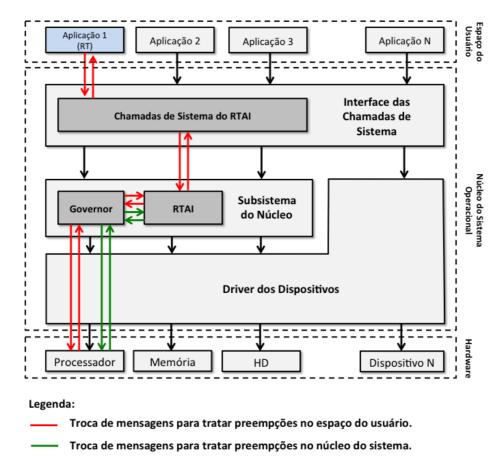

A Figura 1.2 mostra uma visão geral do método proposto, que consiste na adição de três novos componentes à arquitetura do sistema operacional, são eles:

• Chamadas de Sistema do Raw Governor: fornecem as interfaces (API) para que as aplicações de tempo real possam trocar informações com o controlador de tensões e frequências do processador (como por exemplo: as tensões e frequências ideais de cada aplicação). Dessa forma, as aplicações passam ao sistema operacional todas as informações necessárias sobre as tarefas de tempo real que estão em execução no sistema, permitindo assim que as trocas de contexto do processador possam ser feitas diretamente no núcleo do sistema.

<sup>&</sup>lt;sup>1</sup>Overhead é todo e qualquer tempo de computação ou armazenamento que venha a ser gasto para realizar uma determinada tarefa.

Figura 1.2: Visão geral da arquitetura proposta.

Assim, é possível diminuir o tempo de chaveamento de contexto do processador, pois o gerenciamento das tensões e frequências deixam de ser feitas no nível de usuário pelas aplicações e passam a ser feitas no núcleo do sistema operacional com menos *overheads*, ou seja, com menor tempo de resposta;

- Raw Governor: esta é a nova política de gerenciamento do processador com suporte a preempção. Sua função é aplicar as tensões e frequências ideais (informadas pelas aplicações) de forma personalizada de acordo com a tarefa em execução;

- Raw Monitor: esta é uma extensão do *Raw Governor* dentro do escalonador da RTAI. O seu papel é informar ao *Governor* as tarefa que estão retornando de preempção para que seja feito o chaveamento de contexto do processador.

## 1.6 Organização do Trabalho

O material desta dissertação está dividido em capítulos, para o melhor entendimento do trabalho, e a seguir será feito uma breve descrição do que será abordado em cada um deles. No Capítulo 2 serão discutidos os principais conceitos e definições que serão

utilizados no desenvolvimento desta dissertação. No Capítulo 3 serão analisados os principias trabalhos correlatos. No Capítulo 4 será apresentado o método proposto. No Capítulo 5 serão apresentados os resultados experimentais. Por fim, no Capítulo 6 são expostas as conclusões finais, bem como as principais contribuições, limitações e trabalhos futuros.

# Capítulo 2

# Conceitos e Definições

Esta seção apresenta os principais conceitos e definições abordados nesta dissertação, são eles: Sistemas Embarcados, Sistemas de Tempo Real, Escalonamento Dinâmico de Tensão e Frequência (DVFS), Grafo de Fluxo de Controle, *Kernel* do Linux e RTAI. Estes conceitos são fundamentais para que haja um melhor entendimento deste trabalho.

#### 2.1 Sistemas Embarcados

Os sistemas embarcados, na sua grande maioria, possuem *hardwares* mais limitados e, consequentemente, um poder de processamento mais restrito por serem sistemas voltados para aplicações específicas. Durante a fase de projeto desse tipo de sistema é levado em consideração o seu custo, tamanho, desempenho e consumo de energia (Lee *et al.*, 2008).

Esses sistemas estão presentes em quase todo tipo de equipamento eletrônico, como por exemplo: geladeiras, micro-ondas, máquinas de lavar, televisores, celulares, etc. Estes sistemas também são aplicados em ambientes que possuem restrições temporais, como por exemplo: no controle de aviões, no freio de carros, no controle de elevadores, entre outros (Lee et al., 2008).

### 2.2 Sistemas de Tempo Real

Os sistemas de tempo real possuem restrições temporais a serem cumpridas por suas tarefas. Esses sistemas não dependem apenas dos resultados computados, mas também do instante de tempo em que esses resultados foram produzidos (Cheng, 2002), pois necessitam respeitar as restrições temporais impostas para cada tarefa em execução. Os sistemas de tempo real podem ser classificados de duas formas:

- Sistemas de tempo real crítico (*Hard real-time*): requer que todas as tarefas ou suas instâncias concluam suas execuções dentro do prazo especificado, caso contrário os prejuízos serão catastróficos, como por exemplo: um avião poderá cair, o freio de um carro poderá não funcionar, entre outros graves problemas.

- Sistemas de tempo real não-críticos (Soft real-time): permite que algumas de suas tarefas ou suas instâncias percam seus prazos, sem grandes prejuízos para o funcionamento do sistema, como por exemplo: a perda de algum pacote de streaming na transmissão de áudio e vídeo.

#### 2.2.1 Modelo de Tarefas e suas Propriedades Temporais

No contexto de sistemas de tempo real, as tarefas podem ser classificadas de três formas, são elas:

- Periódicas: são tarefas que possuem várias instâncias ou iterações, onde seus períodos são fixos entre duas execuções consecutivas da mesma tarefa;

- Esporádicas: são tarefas que possuem zero ou mais instâncias e existe um intervalo de tempo mínimo entre duas execuções consecutivas da mesma tarefa;

- Aperiódicas: são tarefas que não possuem um intervalo mínimo ou máximo entre duas execuções da mesma tarefa, ou seja não possui um prazo específico para ativação da tarefa, como por exemplo: o aparecimento de um objeto em uma tela de radar.

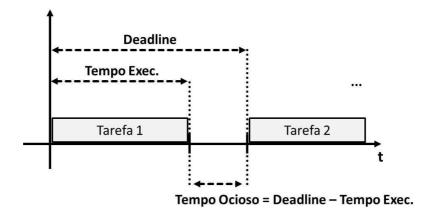

Dentro do contexto temporal, as tarefas possuem as seguintes propriedades (ver Figura 2.1):

- *Deadline* ou Meta Temporal: é o intervalo de tempo máximo que a tarefa terá para concluir o seu processamento, além dos tempos de bloqueio e precedências;

- Tempo de Execução ou Tempo de Computação: é o intervalo de tempo que a tarefa levou para concluir seu processamento;

- Tempo Ocioso ou Tempo de Folga: é o intervalo de tempo não utilizado pela tarefa, ou seja, é a diferença entre a meta temporal (deadline) e o seu tempo de execução. Caso este valor seja negativo, implica dizer que a meta temporal da tarefa foi violada.

Dessa forma, as tarefas ainda podem ser representadas como sendo a tripla  $(c_i, p_i, d_i)$ , onde  $c_i$  é o tempo de computação da tarefa,  $p_i$  é o período e  $d_i$  é a sua meta temporal.

Figura 2.1: Visão geral das premissas temporais associadas a uma tarefa de tempo real.

Com base nessas características é possível extrair o fator de utilização do sistema, que é descrito na Equação 2.1 onde n é o número de tarefas.

$$U = \sum_{i=1}^{n} \frac{c_i}{p_i} \tag{2.1}$$

#### 2.2.2 Relação de Precedência e de Exclusão Mútua

A grande maioria das aplicações de tempo real possuem implicações semânticas entre as tarefas. Tais implicações podem restringir a ordem de execução, como é o caso das relações de precedência. Uma tarefa  $\tau_i$  é dita preceder a tarefa  $\tau_j$  ( $\tau_i \to \tau_j$ ), se  $\tau_j$  somente puder iniciar sua execução após o término da tarefa  $\tau_i$ .

Outra relação importante a ser considerada no escalonamento de tempo real, é a relação de exclusão mútua. Tal relação ocorre quando existe algum recurso compartilhado em exclusão mútua. Dessa forma, temos que uma tarefa  $\tau_i$  exclui  $\tau_j$  quando a execução de uma seção crítica de  $\tau_j$ , que manipula o recurso compartilhado, não pode executar porque  $\tau_i$  ainda está utilizando o recurso.

Portanto, as relações de precedência e de exclusão mútua entre as tarefas integrantes ao problema são especificadas a partir da definição do modelo de tarefas.

#### 2.2.3 Algoritmo de Escalonamento

Antes de abordar sobre o algoritmo de escalonamento de tempo real é necessário ter o conhecimento claro dos seguintes conceitos: escalonamento, escala e escalonador. A política de escalonamento é a forma ou a maneira de ordenar as tarefas que encontram-se disponíveis na fila de prontos. A escala é uma lista ordenada que indica a

ordem de ocupação do processador pelas tarefas "prontas". O escalonador é o componente do sistema operacional responsável por realizar a gestão do processador, além de implementar uma política de escalonamento de tarefas para realizar a ocupação do mesmo.

As políticas de escalonamento definem as regras que irão produzir as escalas, a fim de atender às restrições temporais impostas pelo modelo de tarefas. Essas políticas de escalonamento para sistemas de tempo real podem ser classificadas como:

- Análise Dinâmica (Online): podem sofrer mudanças em tempo de execução, ou seja, os parâmetros podem ter seus valores alterados com a evolução do sistema.

- Análise Estática (Offline): são determinadas em fase de projeto, ou seja, os parâmetros que definem o cálculo de escala são fixas e definidas em tempo de projeto.

Nesse contexto, as tarefas de tempo real ainda podem ser classificadas como:

- Tarefas Preemptivas: são tarefas que podem ser interrompidas por tarefas de maior prioridade.

- Tarefas Não-Preemptivas: são tarefas que não podem ser interrompidas por nenhuma outra tarefa.

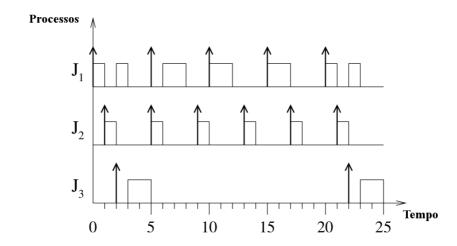

Nesta dissertação, a política de escalonamento utilizada será a *Rate-Monotonic*, também conhecida como RM. Segundo Cheng (2002), o *Rate-Monotonic* é a política de escalonamento de tempo real mais popular, cujo o objetivo é escalonar tarefas periódicas de prioridade fixa. A RMS executa com maior prioridade a instância da tarefa pronta de período mais curto. Em caso de empate entre duas ou mais tarefas, a RMS selecionará aleatoriamente uma para a próxima execução.

**Exemplo.** Considerando três tarefas periódicas com os seguintes tempos de chegada (S), tempos de computação (c), períodos (p) e deadlines (d):

$$\tau_1: S_1 = 0; c_1 = 2; p_1 = d_1 = 5;$$

$$\tau_2: S_2 = 1; c_2 = 1; p_2 = d_2 = 4;$$

$$\tau_3: S_3 = 2; c_3 = 2; p_3 = d_3 = 20;$$

(2.2)

Para esse grupo de tarefas, temos que no instante de tempo 0,  $\tau_1$  é a única tarefa pronta que está programada para ser executada. No instante de tempo 1,  $\tau_2$  chega. Desde que  $p_2 < p_1$ ,  $\tau_2$  tem maior prioridade, então  $\tau_1$  é preemptada e  $\tau_2$  inicia sua execução. No instante de tempo 2,  $\tau_2$  termina sua execução e chega  $\tau_3$ . Como  $p_3 > p_1$ ,  $\tau_1$  agora tem a

maior prioridade, por isso, continua a execução. No instante de tempo 3,  $\tau_1$  termina a execução. Neste momento,  $\tau_3$  é a única tarefa pronta, então ela inicia sua execução. No instante de tempo 4,  $\tau_3$  ainda é a única tarefa, então ela continua a executar até terminar sua execução no instante de tempo 5. Nesse momento, as segundas instâncias de  $\tau_1$  e  $\tau_2$ estão prontas para executar novamente. Como  $p_2 < p_1, \tau_2$  tem a maior prioridade, então  $au_2$  inicia a sua execução. No instante de tempo 6, a segunda instância de  $au_2$  termina a sua execução. Neste momento, a segunda instância  $\tau_1$  é a única tarefa pronta para começar sua execução, terminando no instante de tempo 8. Esse processo segue até o instante de tempo igual ao MMC (em português, Mínimo Múltiplo Comum) dentre os períodos de todas as tarefas, que neste caso é o MMC(4,5,20) = 20. Em outras palavras, a partir do instante de tempo 20 o escalonamento irá se repetir, não sendo mais necessário continuar realizando a geração da escala de execução das tarefas. Esse instante de tempo também é conhecido na literatura como hiper período<sup>1</sup> (em inglês, Hyperperiod). A Figura 2.2 ilustra o diagrama de temporização das tarefas  $J_i$ , segundo a política de escalonamento RM, bem como o instante de tempo que ocorre a repetição do escalonamento (no instante de tempo igual a 20) (Cheng, 2002).

Figura 2.2: Exemplo de uma escala de tarefas  $J_i$  utilizando a política de escalonamento Rate-Monotonic (Cheng, 2002).

Esse processo de geração do diagrama de temporização das tarefas pode ser muito trabalhoso, dependendo da quantidade de tarefas e suas propriedades temporais. Na próxima seção serão abordados alguns testes de escalonabilidade para saber se um dado grupo de tarefas de tempo real é ou não escalonável.

#### 2.2.4 Teste de Escalonabilidade

O teste de escalonabilidade é uma das etapas mais importantes do processo de escalonamento, pois ele irá determinar se um determinado grupo de tarefas é ou não

$<sup>^{1}</sup>$ O hiper período é o instante de tempo no qual a escala de execução das tarefas, dentro do escalonador, se repete.

escalonável, antes de se definir uma escala factível (ver Figura 2.2). Esses testes têm como objetivo analisar situações de picos do sistema no pior caso de execução das tarefas e essas análises vão depender diretamente do modelo de tarefas considerado e da política de escalonamento definida para o problema em questão.

Basicamente, existem três tipos de classificações para testes de escalonabilidade, são eles:

- Suficiente: se o teste for positivo, garante que o conjunto de tarefas é sempre escalonável, caso negativo ainda podem existir um ou mais conjuntos de tarefas escalonáveis;

- Necessário: se o teste for negativo, garante que o conjunto de tarefas é sempre não escalonável;

- Exato: os testes de escalonabilidade exatos são mais complexos e determinam se um dado conjunto de tarefas é ou não escalonável.

Segundo Cheng (2002), existem quatro tipos de teste de escalonabilidade para política RM, são eles:

Teste de Escalonabilidade 1: Dado um conjunto de N tarefas independentes, preemptivas e periódicas sobre um único processador de tal forma que seus deadlines sejam iguais ou maiores do que seus respectivos períodos, desde que eles sejam números inteiros múltiplos entre si, e considerando U a utilização total do modelo de tarefas definido. Uma condição necessária e suficiente para um escalonamento viável desse conjunto de tarefas é definido por:

$$U = \sum_{i=1}^{n} \frac{c_i}{p_i} \le 1 \tag{2.3}$$

Exemplo. Considerando o modelo de tarefas definido na Equação 2.4.

$$\tau_1: S_1 = 0; c_1 = 2; p_1 = d_1 = 5;$$

$$\tau_2: S_2 = 1; c_2 = 1; p_2 = d_2 = 4;$$

$$\tau_3: S_3 = 2; c_3 = 2; p_3 = d_3 = 20;$$

(2.4)

Temos que os períodos das tarefas são múltiplos exatos entre si  $(p_2 < p_1 < p_3, p_1 = 2p_2, p_3 = 4p_2 = 2p_1)$  e que este conjunto de tarefas pertence a classe especial de tarefas definidos pelo teste de escalonabilidade 1. Sendo assim,  $U = \frac{1}{4} + \frac{1}{2} + \frac{2}{8} = 1 \le 1$ , logo esse modelo de tarefas é escalonável pela política RM.

Teste de Escalonabilidade 2: Dado um conjunto de N tarefas independentes, preemptivas e periódicas sobre um único processador, sendo U a utilização total do

modelo de tarefas definido. Uma condição suficiente para o escalonamento viável deste conjunto de tarefas é  $U \leq n(2^{\frac{1}{n}}-1)$

No entanto, o uso desse simples teste de escalonabilidade pode subutilizar o sistema, permitindo que um dado conjunto de tarefas exceda o limite de utilização e ainda possa ser escalonável pela política RM. Portanto, passamos a derivar uma condição suficiente e necessária para o escalonador usando o algoritmo RM. Suponha que temos três tarefas, todos iniciando no instante de tempo 0. A tarefa  $\tau_1$  tem o menor período, seguido por  $\tau_2$  e  $\tau_3$ . É intuitivo ver que  $\tau_1$  terá um escalonamento viável, se o tempo de computação for inferior ou igual ao seu período, portanto, a condição necessária e suficiente deve ser:

$$c_i \le p_i \tag{2.5}$$

Para  $\tau_2$  terá um escalonamento viável, é preciso encontrar um tempo disponível suficiente no intervalo de  $[0, p_2]$  que não seja usado por  $\tau_1$ . Supondo que  $\tau_2$  conclua a sua execução no tempo t. Em seguida, o número total de iterações de  $\tau_1$  no intervalo de [0, t] é:

Para garantir que  $\tau_2$  possa concluir sua execução no tempo t, cada iteração de  $\tau_1$  no intervalo de [0,t] deve ser preenchida e deve haver tempo disponível suficiente para  $\tau_2$  termine a sua execução. Este tempo disponível é  $c_2$ . Portanto, temos:

$$t = \left\lceil \frac{t}{p_1} \right\rceil c_1 + c_2 \tag{2.7}$$

Da mesma forma, deve ser feito para  $\tau_3$ , onde deve haver tempo suficiente restante para executar  $\tau_3$  antes do escalonamento de  $\tau_1$  e  $\tau_2$ :

$$t = \left\lceil \frac{t}{p_1} \right\rceil c_1 + \left\lceil \frac{t}{p_2} \right\rceil c_2 + c_3 \tag{2.8}$$

A próxima questão é como determinar o tempo t de forma que exista um escalonamento viável para que um conjunto de tarefas possa ser construído. Note que há um número infinito de pontos em cada intervalo, se for assumido um tempo não discreto. No entanto, o valor do limite máximo é definido pela Equação 2.6.

Esse valor somente muda em múltiplos de  $p_1$ , com o aumentar de  $c_1$ . Então é necessário apenas mostrar que existe um valor k, tal que:

$$kp_1 \ge kc_1 + c_2 \quad e \quad kp_1 \le p_2$$

(2.9)

Portanto, é preciso verificar que:

$$t \ge \left\lceil \frac{t}{p_1} \right\rceil c_1 + c_2 \tag{2.10}$$

para algum t que seja múltiplo de p1, tal que  $t \leq p_2$ . Se este valor for encontrado, então nós temos a condição necessária e suficiente para um escalonamento viável de  $\tau_2$  usando o algoritmo RM. Esta verificação é finita, uma vez que existe um número finito múltiplo de  $p_1$  que são menores ou iguais a  $p_2$ . Seguindo o mesmo processo para  $\tau_3$ , é necessário verificar se a seguinte condição é válida:

$$t \ge \left\lceil \frac{t}{p_1} \right\rceil c_1 + \left\lceil \frac{t}{p_2} \right\rceil c_2 + c_3 \tag{2.11}$$

Com base nessas condições, é possível definir a condição necessária e suficiente para o escalonamento viável de uma tarefa periódica (ver teste de escalonabilidade 3).

Teste de Escalonabilidade 3: Com base nas condições anteriores, podemos definir uma equação de teste de escalonabilidade iterativa (ver Equação 2.12).

$$w_i(t) = \sum_{k=1}^{i} c_k \left\lceil \frac{t}{p_k} \right\rceil, \quad 0 < t \le p_i$$

(2.12)

Onde,

$$w_i(t) \le t \tag{2.13}$$

e qualquer instante de tempo t é escolhido da seguinte forma:

$$t = kp_j;$$

$$j = 1, ..., i;$$

$$k = 1, ..., \left| \frac{p_i}{p_j} \right|;$$

$$(2.14)$$

Portanto, se e somente se a tarefa  $\tau_i$  é escalonável pela política RM, se  $d_i \neq p_i$  então podemos substituir  $p_i$  pelo  $min(d_i, p_i)$  na Equação 2.14.

O exemplo a seguir aplica esta condição suficiente e necessária para verificar a escalonabilidade de quatro tarefas usando o algoritmo RM.

*Exemplo*. Considerando que todas as tarefas periódicas chegam no instante de tempo 0 e que o período de cada tarefa é igual ao seu *deadline*.

$$\tau_1 : c_1 = 10; p_1 = d_1 = 50;$$

$$\tau_2 : c_2 = 15; p_2 = d_2 = 80;$$

$$\tau_3 : c_3 = 40; p_3 = d_3 = 110;$$

$$\tau_4 : c_4 = 50; p_4 = d_4 = 190;$$

(2.15)

Usando o teste de escalonabilidade 2, passamos a verificar se cada tarefa é escalonável usando o algoritmo RM, começando com as tarefas que têm o menor período.

Para  $\tau_1, i = 1, j = 1, ..., i = 1$ , então:

$$k = 1, ..., \left\lfloor \frac{p_i}{p_j} \right\rfloor = 1, ..., \left\lfloor \frac{50}{50} \right\rfloor = 1;$$

(2.16)

Assim,  $t = kp_1 = 1(50) = 50$ . A tarefa  $\tau_1$  é RM escalonável se e somente se:

$$c_1 \le 50;$$

(2.17)

Portanto,  $c_1 = 10 \le 50$ ,  $\tau_1$  é RM escalonável.

Para  $\tau_2$ , i = 2, j = 1, ..., i = 1, 2, então:

$$k = 1, ..., \left| \frac{p_i}{p_j} \right| = 1, ..., \left\lfloor \frac{80}{50} \right\rfloor = 1;$$

(2.18)

Assim,  $t = 1p_1 = 1(50) = 50$ , ou  $t = 1p_2 = 1(80) = 80$ . A tarefa  $\tau_2$  é RM escalonável se e somente se:

$$c_1 + c_2 \le 50; ou$$

$2c_1 + c_2 \le 80;$  (2.19)

Portanto,  $c_1 = 10$  e  $c_2 = 15, 10 + 15 \le 50$  (ou  $2(10) + 15 \le 80$ ), então  $\tau_2$  é RM escalonável junto com  $\tau_1$ .

Para  $\tau_3$ , i = 3, j = 1, ..., i = 1, 2, 3, então:

$$k = 1, ..., \left| \frac{p_i}{p_j} \right| = 1, ..., \left| \frac{110}{50} \right| = 1, 2;$$

(2.20)

Assim,  $t = 1p_1 = 1(50) = 50$ , ou  $t = 1p_2 = 1(80) = 80$ , ou  $t = 1p_3 = 1(110) = 110$ , ou  $t = 2p_1 = 2(50) = 100$ . A tarefa  $\tau_3$  é RM escalonável se e somente se:

$$c_1 + c_2 + c_3 \le 50; ou$$

$2c_1 + c_2 + c_3 \le 80; ou$

$2c_1 + 2c_2 + c_3 \le 100; ou$

$3c_1 + 2c_2 + c_3 \le 110;$  (2.21)

Portanto,  $c_1 = 10$ ,  $c_2 = 15$  e  $c_3 = 40$ , teremos  $2(10) + 15 + 40 \le 80$  (ou  $2(10) + 2(15) + 40 \le 100$  ou  $3(10) + 2(15) + 40 \le 110$ ). Logo  $\tau_3$  é RM escalonável junto com  $\tau_1 e \tau_2$ .

Para  $\tau_4$ , i = 4, j = 1, ..., i = 1, 2, 3, 4, então:

$$k = 1, ..., \left| \frac{p_i}{p_j} \right| = 1, ..., \left| \frac{190}{50} \right| = 1, 2, 3;$$

(2.22)

Assim,  $t = 1p_1 = 1(50) = 50$ , ou  $t = 1p_2 = 1(80) = 80$ , ou  $t = 1p_3 = 1(110) = 110$ , ou  $t = 1p_4 = 1(190) = 190$ , ou  $t = 2p_1 = 2(50) = 100$ , ou  $t = 2p_2 = 2(80) = 160$ , ou  $t = 3p_1 = 3(50) = 150$ . A tarefa  $\tau_4$  é RM escalonável se e somente se:

$$c_{1} + c_{2} + c_{3} + c_{4} \leq 50; ou$$

$$2c_{1} + c_{2} + c_{3} + c_{4} \leq 80; ou$$

$$2c_{1} + 2c_{2} + c_{3} + c_{4} \leq 100; ou$$

$$3c_{1} + 2c_{2} + c_{3} + c_{4} \leq 110; ou$$

$$3c_{1} + 2c_{2} + 2c_{3} + c_{4} \leq 150; ou$$

$$4c_{1} + 2c_{2} + 2c_{3} + c_{4} \leq 160; ou$$

$$4c_{1} + 3c_{2} + 2c_{3} + c_{4} \leq 190;$$

$$(2.23)$$

Substituindo os valores de  $c_1, c_2, c_3$  e  $c_4$  na Equação 2.23, temos que nenhuma das equações podem ser satisfeita. Logo  $\tau_4$  não é RM escalonável. Isto é um fato, pois:

$$U = \frac{10}{50} + \frac{15}{80} + \frac{40}{110} + \frac{50}{190} = 1,014 > 1$$

(2.24)

Portanto, nenhum escalonador poderá escalonar estas tarefas. Agora, se a tarefa  $\tau_4$  for ignorada, a utilização passará a ser U=0,75, que já satisfaz o teste de Escalonabilidade 2. Sendo assim, a Figura 2.3 mostra a escala de execução das três primeiras tarefas.

Teste de Escalonabilidade 4: Segundo Bertolotti e Manduchi (2012), essa é uma outra forma de representar a equação iterativa do teste de escalonabilidade da política RM. Assumindo que:

Figura 2.3: Representação da escala de execução das tarefas  $\tau_1, \tau_2$  e  $\tau_3$ .

$$w_i^0 = c_i \quad e$$

$$w_i^{x+1} = c_i + \sum_{k \in hp(i)} c_k \left\lceil \frac{w_i^x}{p_k} \right\rceil$$

(2.25)

onde hp(i) é o conjunto de tarefas com prioridades superiores a prioridade da tarefa  $\tau_i$ . Esse sistema só possui solução se o resultado do tempo de resposta da iteração x+1 convergir e for igual a iteração x, ou seja  $(w_i^{x+1}=w_i^x)$ , e se o tempo de resposta  $w_i^{x+1} \leq d_i$ . Caso contrário, as tarefas não são RM escalonáveis.

*Exemplo*. Considerando que todas as tarefas periódicas chegam no instante de tempo 0 e que o período de cada tarefa é igual ao seu *deadline*.

$$\tau_1 : c_1 = 3; p_1 = d_1 = 7;$$

$$\tau_2 : c_2 = 3; p_2 = d_2 = 12;$$

$$\tau_3 : c_3 = 5; p_3 = d_3 = 20;$$

(2.26)

Usando o teste de escalonabilidade da Equação 2.25 e começando com as tarefas que têm o menor período.

Para  $\tau_1$ , temos:

$$w_1^0 = c_1 \to w_1^0 = 3 (2.27)$$

Como  $w_1^0 \le d_1 \to 3 \le 7$ , logo  $\tau_1$  é RM escalonável.

Para  $\tau_2$ , temos:

$$w_2^0 = c_2 = 3;$$

$$w_2^1 = c_2 + c_1 \left\lceil \frac{w_2^0}{p_1} \right\rceil = 3 + 3 \left\lceil \frac{3}{7} \right\rceil = 6;$$

$$w_2^2 = c_2 + c_1 \left\lceil \frac{w_2^1}{p_1} \right\rceil = 3 + 3 \left\lceil \frac{6}{7} \right\rceil = 6;$$

(2.28)

Como  $w_2^2 = w_2^1$  e  $w_2^2 \leq d_2 \, \to \, 6 \leq 12$ , logo  $\tau_2$  é RM escalonável.

Para  $\tau_3$ , temos:

$$w_{3}^{0} = c_{3} = 5;$$

$$w_{3}^{1} = c_{3} + c_{1} \left\lceil \frac{w_{3}^{0}}{p_{1}} \right\rceil + c_{2} \left\lceil \frac{w_{3}^{0}}{p_{2}} \right\rceil = 5 + 3 \left\lceil \frac{5}{7} \right\rceil + 3 \left\lceil \frac{5}{12} \right\rceil = 11;$$

$$w_{3}^{2} = c_{3} + c_{1} \left\lceil \frac{w_{3}^{1}}{p_{1}} \right\rceil + c_{2} \left\lceil \frac{w_{3}^{1}}{p_{2}} \right\rceil = 5 + 3 \left\lceil \frac{11}{7} \right\rceil + 3 \left\lceil \frac{11}{12} \right\rceil = 14;$$

$$w_{3}^{3} = c_{3} + c_{1} \left\lceil \frac{w_{3}^{2}}{p_{1}} \right\rceil + c_{2} \left\lceil \frac{w_{3}^{2}}{p_{2}} \right\rceil = 5 + 3 \left\lceil \frac{14}{7} \right\rceil + 3 \left\lceil \frac{14}{12} \right\rceil = 17;$$

$$w_{3}^{4} = c_{3} + c_{1} \left\lceil \frac{w_{3}^{3}}{p_{1}} \right\rceil + c_{2} \left\lceil \frac{w_{3}^{3}}{p_{2}} \right\rceil = 5 + 3 \left\lceil \frac{17}{7} \right\rceil + 3 \left\lceil \frac{17}{12} \right\rceil = 20;$$

$$w_{3}^{5} = c_{3} + c_{1} \left\lceil \frac{w_{3}^{4}}{p_{1}} \right\rceil + c_{2} \left\lceil \frac{w_{3}^{4}}{p_{2}} \right\rceil = 5 + 3 \left\lceil \frac{20}{7} \right\rceil + 3 \left\lceil \frac{20}{12} \right\rceil = 20;$$

Como  $w_3^5=w_3^4$  e  $w_3^5\leq d_3\to 20\leq 20$ , logo  $\tau_3$  é RM escalonável. Portanto, o grupo de tarefas é RM escalonável.

# 2.3 Escalonamento Dinâmico de Tensão e Frequência (DVFS)

Atualmente, a técnica DVFS só é possível devido a grande maioria dos processadores utilizarem as tecnologias CMOS (em inglês, Complementary Metal Oxide Semiconductor) e MOSFET (em inglês, Metal Oxide Semiconductor Field Effect Transistor), pois elas permitem controlar via software as tensões e frequências que são utilizadas pelo processador, permitindo que sejam feitas trocas constantes de frequência à medida que o sistema necessite de mais ou menos processamento (Kang e Leblebici, 2002).

Há vários processadores disponíveis no mercado que visam o baixo consumo de energia, onde é possível associar para um determinado nível de tensão um determinado nível de frequência. A Tabela 2.1 mostram as tensões e frequências do processador AMD Athlon II X2 250, por exemplo para se alcançar uma frequência de  $3.000\,MHz$  é necessário aplicar uma tensão de  $1,425\,V$  no processador que irá consumir uma potência de  $60,2\,W$ , essa interpretação se aplica as demais linhas da tabela (AMD, 2009).

O surgimento dessa técnica permitiu que os sistemas operacionais passassem a estabelecer políticas pré-definidas para realizar o gerenciamento dinâmico das tensões e

Tensões (V) Potência (W) Frequências (MHz) 3000 1,425 60,2 2300 1.325 51.21800 1,225 37,2 800 1,125 23,1

Tabela 2.1: Lista de tensões e frequências do processador AMD Athlon II X2 250.

frequências utilizadas pelo processador (Kim *et al.*, 2008; Baums e Zaznova, 2008). Dentro do contexto de sistemas de tempo real, as duas principais técnicas DVFS voltadas para o baixo consumo de energia do processador são (Quinõnes *et al.*, 2011; Lee *et al.*, 2008):

- **DVFS intra-tarefa:** as tensões e frequências são definidas pelas tarefas de tempo real, levando em consideração apenas os dados locais da aplicação. Uma das formas de se obter essas tensões e frequências é através das análises estáticas do grafo de fluxo de controle (em inglês, *Control-Flow Graph* CFG), ver mais detalhes na Seção 2.4.

- DVFS inter-tarefa: as tensões e frequências são definidas tarefa por tarefa a cada instante de atuação do escalonador do sistema, levando em consideração as informações de todas as tarefas em execução no sistema. A principal diferença com a técnica intra-tarefa é que os tempos de folga (ver definição na Seção 2.2.1) obtidos com a técnica inter-tarefa podem ser usados na tarefa atual ou nas tarefas seguintes, enquanto que os tempos de folga obtidos com a técnica intra-tarefa só poderão ser utilizados pelas tarefas que as gerou.

#### 2.4 Grafo de Fluxo de Controle

Os grafos de fluxo de controle são abstrações estáticas do fluxo de execução de uma determinada aplicação, extraídos a partir do código fonte. O CFG é um grafo direcionado e a resposta de saída da execução da aplicação vai depender do caminho percorrido nesse grafo (Lee et al., 2008). Os componentes básicos de uma CFG são:

- Blocos Básicos: são trechos de código no qual a aplicação não possui nenhum desvio condicional.

- Blocos de Desvio: s\(\tilde{a}\) o trechos de c\(\tilde{d}\)igo que correspondem a desvios condicionais

e desvios incondicionais.

- Arestas: representam as relações de dependência entre cada bloco ou nó.

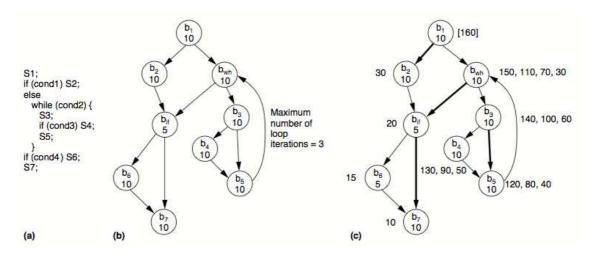

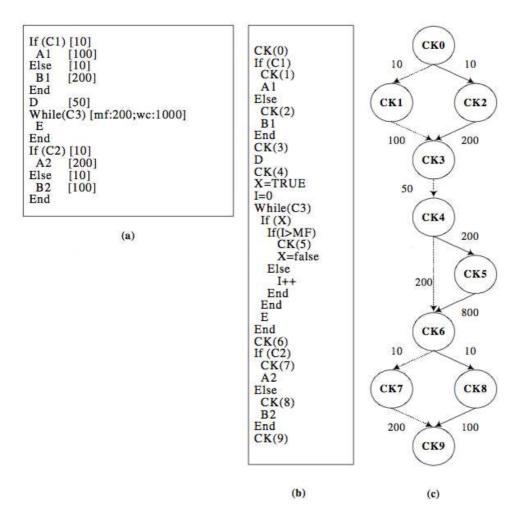

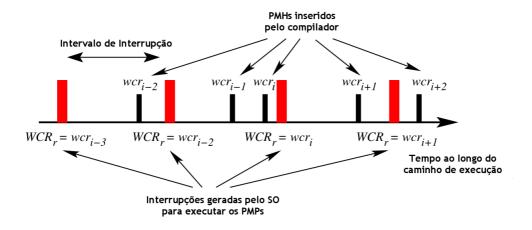

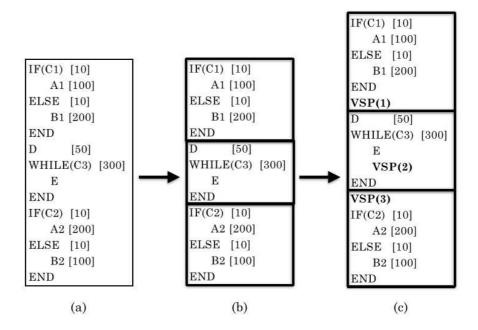

A Figura 2.4 mostra um exemplo de como é feita a extração do grafo de fluxo de controle de uma aplicação. Vale destacar que os  $b_i$ , do item b da figura, contém os trechos de código da aplicação agrupados de acordo com os desvios condicionais, ou seja,  $b_2$  possui os trechos de código da primeira condição, b<sub>6</sub> da terceira condição e assim sucessivamente. Além disso, cada  $b_i$  possui um peso, que indica a quantidade de ciclos de execução no pior caso. Essa informação será utilizada no item c para calcular o pior caso de execução da aplicação no geral, ou seja, assumindo o pior caminho de execução como  $b_1, b_{wh}, b_3, b_4, b_5, b_{wh}, b_3, b_4, b_5, b_{wh}, b_3, b_4, b_5, b_{wh}, b_{if}, b_6$  e  $b_7$  resultará em um total de 160 ciclos, somando os custos de cada nó. A partir dessa estimativa, o grafo do item c também tem o objetivo de mostrar ao lado de cada nó a quantidade de ciclos que faltam para a aplicação ser concluída, exemplo: estando em  $b_1$  e levando em consideração o pior caminho de execução a quantidade de ciclos restantes é 160; passando o fluxo de execução para  $b_{wh}$ , que possui um custo de 10 ciclos, a quantidade restante passa a ser 150 ciclos; e assim sucessivamente até que todo o código seja executado. Dessa forma, é possível ter um controle da quantidade de ciclos restantes à medida que a aplicação vai sendo executada.

Figura 2.4: Processo de extração do grafo de fluxo de controle de uma aplicação, onde: (a) Mostra o seu código fonte; (b) O CFG extraído a partir do código fonte e seus componentes básicos; e (c) Mostra o processo de análise da quantidade de ciclos de execução da tarefa no pior caso (Shin e Kim, 2001).

#### 2.5 Kernel do Linux

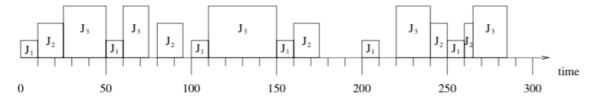

O Kernel é o núcleo de qualquer sistema operacional, em outras palavras, é o componente central que visa estabelecer uma ligação entre as aplicações e o processamento dos dados no nível do hardware. As principais responsabilidades do Kernel são realizar o gerenciamento do escalonamento dos processos, gerenciar as memórias e os dispositivo de entrada e saída, além de prover um encapsulamento de acesso para todos os componentes de hardware (Cheng, 2002). Dentre os principais

componentes e recursos utilizados nesta dissertação (ver Figura 2.5), será feito um breve resumo sobre os seguintes tópicos: Escalonador, Chamadas de Sistema e Módulo CPUFreq.

Figura 2.5: Visão geral dos principais componentes e recursos do *Kernel* do Linux utilizados nesta dissertação.

#### 2.5.1 Escalonador

Dentre todos os componentes presentes no *Kernel*, um dos mais importantes é o escalonador. Ele é a base de funcionamento de qualquer sistema operacional e seu papel é decidir qual processo será executado, quando e por quanto tempo ele ficará executando no processador (Love, 2010). Todo escalonador possui um algoritmo de escalonamento (ver Subseção 2.2.3), que podem ser: (1) não preemptivo, quando os processos executam até o fim sem ser interrompidos; e (2) preemptivo, quando os processos executam em fatias de tempo (chamadas de *quantum*) definidas pelo sistema operacional. Esse componente é útil para o método proposto, pois nele será introduzido um monitor de tarefas que terá o objetivo de auxiliar o *Governor* nas trocas de tensões e frequências do processador quando ocorrerem preempções entre as tarefas em tempo real.

#### 2.5.2 Chamadas de Sistema

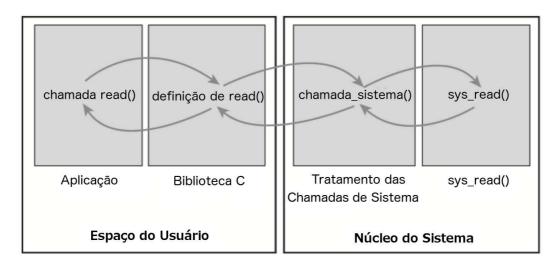

As chamadas de sistema (em inglês, System Calls) têm a função de estabelecer uma comunicação entre o espaço do usuário (em inglês, Userspace) e o núcleo do sistema operacional (em inglês, Kernelspace). Elas fornecem um conjunto de interfaces que possibilitam os processos em execução interagirem com o sistema. Através das chamadas de sistema é possível criar novos processos, se comunicar com outros processos, obter informações do sistema operacional, dentre outros recursos.

Essas interfaces agem como mensageiros entre as aplicações e o núcleo do sistema operacional, além de servir como peça chave para garantir a estabilidade do sistema, impedindo que as aplicações fiquem livres para fazerem o que quiserem dentro do núcleo do sistema (Cheng, 2002). A Figura 2.6 mostra o processo de execução de uma chamada de sistema, desde a função no nível de usuário até ela ser executada no núcleo do sistema operacional.

Figura 2.6: Visão geral do processo de execução de uma chamada de sistema no Linux (Cheng, 2002).

Dentro da método proposto nesta dissertação, as chamadas de sistema irão estabelecer a comunicação entre as aplicações de tempo real e o controlador de tensões e frequências do sistema operacional (*Governor*), para que ele possa realizar o gerenciamento do processador de acordo com a aplicação em execução no sistema.

#### 2.5.3 Módulo CPUFreq

O módulo CPUFreq é o responsável por realizar o escalonamento de tensões e frequências do processador, dentro do *Kernel* do Linux. Esse módulo permite que sejam feitos chaveamentos de contexto do processador de acordo com políticas chamadas de *Governors* (Brodowski e Golde, 2013).

Os Governors são políticas pré-definidas de escalonamento de frequências do processador com propósitos bem específicos. Os principais Governors pré-definidos pelo módulo CPUFreq são (Brodowski e Golde, 2013):

- **Performance**: este *Governor* define estaticamente o processador para a frequência mais alta dentro dos limites permitidos.

- *Powersave*: este *Governor* define estaticamente o processador para a frequência mais baixa dentro dos limites permitidos.

- *Userspace*: este *Governor* permite que o usuário, ou qualquer programa do espaço do usuário, com UID "root" (ou seja, com privilégios de administrador), possam definir uma frequência específica no processador. Dessa forma, o controle das tensões e frequências do processador é feita pela aplicação de tempo real.

- *Ondemand*: este *Governor* é definido dependendo da utilização atual do processador. Para fazer isso, o processador deve ter a capacidade de trocar frequências rapidamente.

- Conservative: este Governor é muito semelhante ao Ondemand, exceto pela maneira de como é feito o incremento e decremento da frequência do processador, pois os saltos de incremente e decremento são menores.

É importante ressaltar que nenhum dos *Governors* citados possuem um canal de comunicação direto com as aplicações do nível de usuário. O único que chega a ter alguma comunicação com o espaço do usuário é o *Userspace Governor*, mas os comandos são feitos via terminal e necessitam de privilégios de administrador do sistema para serem executados.

Portanto, o módulo CPUFreq será a base para a implementação de um novo *Governor*, que realizará o escalonamento das tensões e frequências do processador baseado nos dados informados pelas aplicações de tempo real, de forma *online*.

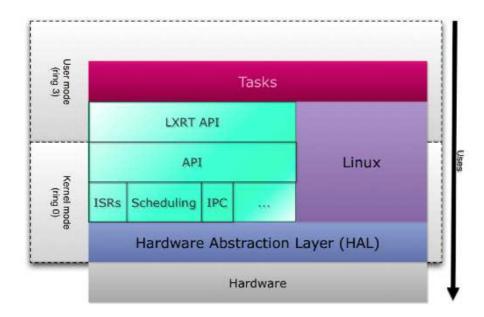

#### 2.6 RTAI

RTAI significa Interface para Aplicações de Tempo Real (em inglês, Real Time Application Interface). Ela surgiu para dar ao Linux o suporte a premissas temporais, mas para isso foi necessário fazer algumas alterações no código fonte do Kernel, principalmente nas políticas de tratamento de interrupção e no escalonador (Bucher et al., 2014), para torná-lo totalmente preemptivo. Dessa forma, é possível obter uma plataforma de tempo real, com uma baixa latência e altas exigências de previsibilidade.

O RTAI oferece os mesmos serviços do núcleo do *Kernel* do Linux, acrescentando as características de um sistema de tempo real industrial (Bucher *et al.*, 2014). Ele consiste basicamente de um despachante de interrupção.